|

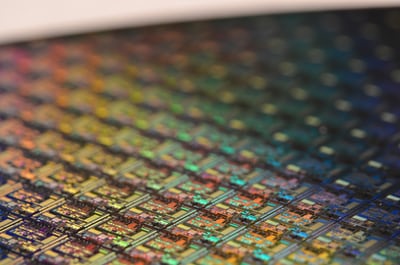

Cell Height is limited by minimum metal pitch, number of metal tracks, and less so fin count and fin pitch. CGP is limited by contact width, spacer width, gate length and diffusion breaks. EUV is needed to shrink the lowest metal layers further. Scaling trends show that the actual transistors themselves (Front End Of Line FEOL) can shrink better than the metal interconnect to wire them (Back End Of Line BEOL). Logic transistor density scaling comes from reducing these two dimensions. Angstronomics will use the following descriptor for node dimensions: This gives the unit cell area which can be used to determine density. The key dimensions to note in transistor area scaling is the Contacted Gate Pitch (CGP, historically poly pitch CPP) in the horizontal x-direction, and Cell Height in the vertical y-direction. Designers build standard logic circuits within these rows like Inverters, NAND gates, adders and flipflop cells that serve Boolean logic functions. Standard cells are organized into horizontal rows. Modern process technology uses Complementary Metal Oxide Semiconductor transistors, mixing PMOS and NMOS to create logic circuits. These assumed numbers have been with us for years, even ASML themselves showed just recently that foundry 5nm is over 180 MTr/mm² (relevant slide at the bottom of this article).ĬMOS FinFET standard cell diagram from imec (SPIE 2019) We will explain how transistor density is calculated below. With nothing else to work with, the density claim was simply multiplied with known TSMC 7nm densities to arrive at numbers like 171 Million Transistors per square mm (MTr/mm²). Since then, TSMC’s public disclosures left us with varying 1st party logic density improvement claims, from 1.7x to 1.84x, leading to many incorrect density assumptions from media and even industry. The paper seemed to have passed muster only because it was about the world’s most advanced process technology. Scotten Jones and David Schor expressed that the paper was more marketing than technical. Their IEDM 2019 paper about N5 was accepted which contained no transistor dimensions. Information for calculating transistor density has not gone far beyond the ‘1.8x vs N7‘ that TSMC said 4 years ago. But some physicists and engineers think we might be bumping up against some fundamental physical limits when it comes to transistor size.TSMC has remained very tight lipped on technical details about N5. These will use transistors measuring a mere 32 nanometers in width. Intel and other microprocessor manufacturers are already working on the next generation of chips. By the 2010s, Intel produced microprocessors with transistors measuring only 45 nanometers wide. But that raises an interesting question: How small can transistors - and by extension, CPUs - get? In 1947, a single transistor measured a little over one-hundredth of a meter high. These days, the number of transistors doubles every 24 months. But it hasn't kept up with the pace Moore observed. Since Moore's observation, the shrinking trend has continued. Without transistors, we would still be using vacuum tubes and mechanical switches to make calculations. It's because of these small transistors that we have electronic devices like personal computers, smartphones and mp3 players. Like clockwork, engineers were finding ways to reduce the size of transistors.

It makes calculations and processes data.īy the 1960s, computer scientist (and Intel co-founder) Gordon Moore made an interesting observation: He noticed that every 12 months, engineers were able to double the number of transistors on a square-inch piece of silicon. If you compare a computer to a human being, the microprocessor would be the brain.

In turn, the integrated circuit paved the way for the development of the microprocessor. In 1958, engineers attached two transistors to a silicon crystal and created the world's first integrated circuit.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed